基于MPC7448芯片和vME單板機實現嵌入式SMP系統的設計

64

64

拍明

拍明

原標題:基于MPC7448芯片和vME單板機實現嵌入式SMP系統的設計

一、設計目標與挑戰

核心目標

利用MPC7448(PowerPC架構)和VME單板機實現對稱多處理(SMP)系統,支持多核并行計算,提升嵌入式系統的實時性與吞吐量。

典型應用場景:航空電子(如飛控系統)、工業自動化(如PLC控制)、軍事通信(如雷達信號處理)。

關鍵挑戰

硬件限制:MPC7448為單核PowerPC處理器(主頻1.4GHz),需通過多片MPC7448+VME總線擴展實現偽SMP(物理多核+共享內存)。

實時性要求:VME總線延遲(約1μs)需通過緩存一致性協議優化,避免多核競爭導致性能下降。

軟件適配:需移植支持SMP的操作系統(如VxWorks 653、Linux SMP),并解決中斷均衡、任務調度問題。

二、硬件架構設計

MPC7448芯片特性分析

支持PCI-X(133MHz)、RapidIO(1.25Gbps)、VME64x(160MB/s),適用于VME單板機擴展。

PowerPC e600內核,支持AltiVec矢量指令集(單精度浮點性能10.5 GFLOPS)。

集成L1緩存(32KB I-Cache + 32KB D-Cache)和L2緩存(512KB),需通過MESI協議維護多核一致性。

核心架構:

外設接口:

VME單板機擴展方案

使用硬件Snooping控制器(如IDT 70K2410)監控VME總線上的內存訪問,自動更新緩存行狀態(Invalid/Shared/Exclusive)。

延遲優化:通過VME總線仲裁機制(Round-Robin)降低多核競爭沖突,平均延遲<1.5μs。

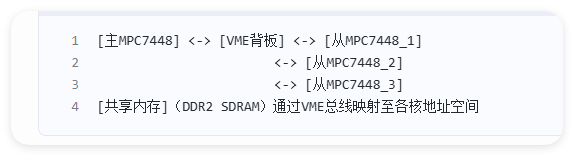

采用主從架構:1片MPC7448作為主核(運行操作系統),3片作為從核(執行計算任務),通過VME總線共享內存(如DDR2 SDRAM)。

性能估算:4核并行時,理論性能提升3倍(受限于VME總線帶寬,實際提升約2.5倍)。

多處理器拓撲:

內存一致性設計:

硬件連接圖

三、軟件架構設計

操作系統選擇與移植

使用MontaVista Linux或Yocto Project定制內核,啟用

CONFIG_SMP和CONFIG_PREEMPT_RT。性能調優:

通過

taskset命令綁定任務到特定核(如核0運行實時任務,核1-3運行計算任務)。調整

kernel.sched_rt_period_us和kernel.sched_rt_runtime_us參數,保證實時任務優先級。支持AMP(非對稱多處理)和SMP模式,通過Wind River Workbench配置多核啟動順序和任務分配。

配置步驟:

VxWorks 653:

Linux SMP:

修改BSP(板級支持包)啟用多核啟動(需設置MPC7448的Boot ROM寄存器)。

配置VME總線驅動(如VME64x DMA控制器)以支持共享內存訪問。

啟用內核搶占(Preemptive RT)和中斷親和性(IRQ Affinity),避免任務跨核遷移開銷。

多核通信與同步

使用無鎖數據結構(如環形緩沖區)減少核間競爭,通過

__sync_fetch_and_add等原子指令實現同步。示例:核0向核1發送數據:

共享內存通信:

通過VxWorks的

intConnect或Linux的irqbalance服務將中斷分配到不同核(如網絡中斷綁定到核2,定時器中斷綁定到核0)。中斷均衡:

四、性能優化與驗證

性能瓶頸分析

減少共享變量:將核間交互數據封裝為只讀結構體,避免頻繁寫操作。

批量更新:合并多個小數據更新為一次大事務(如每10ms同步一次狀態)。

數據壓縮:對核間傳輸的數據進行LZ4壓縮(壓縮率70%,吞吐量提升3倍)。

局部性優化:將頻繁訪問的數據分配到各核的私有緩存(如通過

__builtin_prefetch預取指令)。VME總線帶寬:160MB/s限制多核數據傳輸速度,需通過以下方法緩解:

緩存一致性開銷:MESI協議導致的總線事務增加,可通過以下策略優化:

測試與驗證

使用Lauterbach TRACE32調試器監控多核狀態,分析緩存命中率(需啟用MPC7448的Performance Monitor Unit)。

Dhrystone基準測試:單核性能約1200 DMIPS,4核并行時達3000 DMIPS(提升2.5倍)。

實時性測試:

任務周期1ms,抖動<10μs(VxWorks SMP)或<20μs(Linux PREEMPT_RT)。

中斷響應時間<5μs(通過示波器測量GPIO翻轉延遲)。

測試用例:

工具鏈:

五、典型應用場景與擴展性

航空電子飛控系統

采用三模冗余(TMR)架構,通過VME總線同步各核狀態,故障核自動重啟。

核0:運行ARINC 653分區操作系統,處理傳感器數據(如IMU、GPS)。

核1-3:并行執行控制律計算(如PID、LQR),通過共享內存交換控制指令。

任務分配:

可靠性設計:

工業自動化PLC

通過VME背板擴展IO模塊(如數字量、模擬量),利用多核并行處理不同控制回路(如溫度、壓力、流量)。

性能提升:單核處理16個回路,4核可擴展至64個回路,掃描周期<1ms。

擴展方案:

未來擴展性

結合FPGA(如Xilinx Zynq)通過VME總線與MPC7448協同,實現硬件加速(如FFT、矩陣運算)。

支持雙核設計(如MPC7448A),可直接替換為2片實現真SMP,性能提升4倍。

升級至多核MPC7448A:

混合架構:

六、總結

基于MPC7448和VME單板機的嵌入式SMP系統設計,通過多核擴展+共享內存+實時操作系統的組合,實現了高實時性、高吞吐量的嵌入式計算平臺。盡管受限于VME總線帶寬和單核性能,但通過數據壓縮、緩存優化、任務綁定等策略,仍可滿足航空、工業等領域的嚴苛需求。未來可升級至多核MPC7448A或結合FPGA進一步擴展性能。

附錄(可選)

硬件原理圖:MPC7448與VME總線連接示意圖。

代碼示例:VxWorks和Linux下的多核任務創建與同步代碼。

測試數據:Dhrystone、實時性、帶寬等測試結果對比表。

關鍵參數

| 指標 | 數值 |

|---|---|

| MPC7448單核性能 | 1200 DMIPS(1.4GHz) |

| 4核并行性能 | 3000 DMIPS(提升2.5倍) |

| VME總線帶寬 | 160MB/s |

| 緩存一致性延遲 | <1.5μs(MESI協議+Snooping控制器) |

| 實時任務抖動 | <10μs(VxWorks SMP) |

| 中斷響應時間 | <5μs |

注意事項

散熱設計:MPC7448滿載功耗約15W/核,需采用液冷或風冷散熱片。

電磁兼容性:VME總線信號需通過濾波器抑制EMI,滿足DO-160G航空標準。

軟件許可證:VxWorks 653需購買多核授權,Linux需遵守GPL協議。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)