深入理解晶振,單片機晶振腳原理是什么?

29

29

拍明

拍明

原標題:深入理解晶振,單片機晶振腳原理是什么?

一、晶振的基本概念

1. 定義

晶振(Crystal Oscillator)是一種利用石英晶體的壓電效應產生穩定頻率信號的電子元件。其核心是石英晶體諧振器(Quartz Crystal Resonator),通過外接電路形成振蕩器,為單片機、通信芯片等提供時鐘基準。

2. 壓電效應

正壓電效應:石英晶體在機械應力作用下產生電荷(機械能→電能)。

逆壓電效應:石英晶體在電場作用下產生機械形變(電能→機械能)。

諧振原理:當外接電場頻率與石英晶體的固有機械諧振頻率一致時,晶體發生共振,形成穩定的振蕩信號。

3. 晶振的等效電路

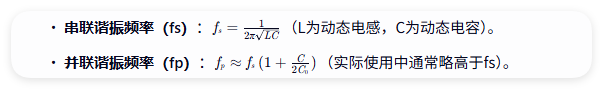

石英晶體可等效為RLC串聯諧振電路與電容C0并聯:

負載電容(CL):晶振的標稱頻率需匹配外部負載電容(如12pF、20pF),以調整實際振蕩頻率。

4. 晶振的分類

無源晶振(Crystal):僅包含石英晶體,需外接振蕩電路(如反相器、電阻、電容)。

有源晶振(Oscillator):內置振蕩電路,直接輸出穩定頻率信號(如方波、正弦波),無需外接元件。

二、單片機晶振腳的作用與原理

1. 晶振腳的作用

單片機的晶振腳(通常標記為XTAL1和XTAL2)用于連接晶振或外部時鐘源,為單片機提供系統時鐘。時鐘信號是單片機執行指令、定時、通信等操作的基礎。

2. 無源晶振的振蕩電路

以常見的皮爾斯振蕩器(Pierce Oscillator)為例,其電路結構如下:

XTAL1:連接晶振的一端和反相器的輸入端。

XTAL2:連接晶振的另一端和反相器的輸出端。

反饋電阻(Rf):通常為1MΩ~10MΩ,用于啟動振蕩并提供偏置電流。

負載電容(CL1、CL2):通常為12pF~22pF,與晶振的負載電容匹配,調整振蕩頻率。

電路原理:

反相器(如單片機內部的CMOS反相器)提供180°相位反轉。

晶振和負載電容構成諧振回路,提供額外的180°相位延遲。

總相位延遲為360°,滿足振蕩條件(巴克豪森準則)。

反饋電阻Rf確保反相器工作在線性區,啟動振蕩。

3. 有源晶振的連接

有源晶振通常有4個引腳:

VCC:電源輸入(如3.3V、5V)。

GND:地。

OUT:時鐘信號輸出(連接單片機的XTAL1或時鐘輸入引腳)。

NC/EN:懸空或使能端(部分型號)。

連接方式:

將有源晶振的OUT引腳直接連接到單片機的時鐘輸入引腳(如XTAL1),無需外接元件。

注意電源電壓匹配和輸出信號電平(如TTL、CMOS)。

三、晶振腳的關鍵參數與設計要點

1. 頻率穩定性

晶振的頻率穩定性(如±10ppm、±50ppm)直接影響單片機的定時精度。

溫度、電壓、負載電容的變化會導致頻率漂移,需選擇合適的晶振類型(如溫度補償晶振TCXO)。

2. 負載電容匹配

晶振的標稱頻率需匹配外部負載電容(CL1 + CL2 + 寄生電容)。

寄生電容(通常為2pF~5pF)需在設計中考慮,可通過調整CL1和CL2的值補償。

計算公式:(通常取C1 = C2)。

3. 啟動時間與功耗

晶振的啟動時間(如1ms~10ms)影響單片機的啟動速度。

驅動電平(Drive Level)需適中,過大可能導致晶振過驅,過小可能導致振蕩不穩定。

4. PCB布局要點

晶振引腳到單片機的走線應盡量短(<5cm),減少寄生電感和電容。

晶振下方避免走線或鋪銅,減少干擾。

負載電容應靠近晶振引腳放置。

四、常見問題與解決方案

1. 晶振不起振

原因:

負載電容不匹配。

反饋電阻過大或過小。

晶振損壞或質量不佳。

PCB布局不合理(如走線過長)。

解決方案:

檢查負載電容值,調整至匹配晶振的CL。

確保反饋電阻在1MΩ~10MΩ范圍內。

更換晶振或測試晶振是否正常(如用示波器觀察輸出波形)。

優化PCB布局,縮短晶振引腳到單片機的走線。

2. 頻率不穩定

原因:

電源噪聲干擾。

溫度變化大。

負載電容變化。

解決方案:

在電源引腳添加去耦電容(如0.1μF陶瓷電容)。

選擇溫度穩定性好的晶振(如TCXO)。

確保負載電容固定,避免焊接不良。

3. 晶振發熱

原因:

驅動電平過大。

晶振質量不佳。

解決方案:

降低驅動電平(如調整反饋電阻或選擇低驅動電平的晶振)。

更換晶振。

五、示例:51單片機晶振電路設計

1. 無源晶振電路

晶振頻率:12MHz

負載電容:22pF(CL1 = CL2 = 22pF)

反饋電阻:1MΩ

電路連接:

XTAL1:晶振一端 + 22pF電容到GND + 1MΩ電阻到XTAL2。

XTAL2:晶振另一端 + 22pF電容到GND。

2. 有源晶振電路

晶振頻率:12MHz

輸出電平:CMOS

電路連接:

VCC:3.3V

GND:GND

OUT:連接XTAL1

NC:懸空

六、總結

晶振的核心:利用石英晶體的壓電效應產生穩定頻率信號。

單片機晶振腳的作用:為單片機提供系統時鐘,通常通過皮爾斯振蕩器連接無源晶振,或直接連接有源晶振。

設計要點:

匹配負載電容,確保頻率穩定。

優化PCB布局,減少干擾。

選擇合適的晶振類型(無源/有源、頻率穩定性)。

常見問題:不起振、頻率不穩定、發熱等,需通過調整元件值、優化布局或更換晶振解決。

通過深入理解晶振的工作原理和單片機晶振腳的設計要點,可以確保系統時鐘的穩定性和可靠性,從而提高單片機的整體性能。

責任編輯:

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)