MOSFET器件的選擇技巧

38

38

拍明

拍明

原標題:MOSFET器件的選擇技巧

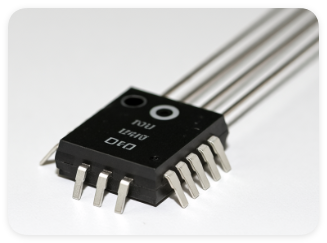

MOSFET(金屬氧化物半導體場效應晶體管)作為功率電子系統的核心器件,其選型直接影響電路的效率、可靠性、成本及動態性能。以下從關鍵參數分析、應用場景適配、失效風險規避三方面,系統闡述MOSFET的選擇邏輯與實用技巧。

一、核心參數解析:MOSFET選型的五大維度

1. 電壓參數:決定器件安全邊界

漏源擊穿電壓(VDSS)

安全裕量:實際工作電壓需≤80% VDSS(如24V系統選VDSS≥30V MOSFET)。

雪崩能量(EAS):感性負載關斷時需承受反向電壓尖峰,需根據負載電感量(L)和電流(I)計算:

案例:

電機驅動電路中,若電感量100μH、峰值電流10A,需EAS≥750mJ(對應VDSS≥60V的器件)。

柵源擊穿電壓(VGSS)

通常±20V~±30V,需避免驅動電壓超過此值(否則柵極氧化層擊穿,器件永久失效)。

2. 電流參數:平衡導通損耗與散熱成本

連續漏極電流(ID)

12V/5A負載,選RDS(ON)=10mΩ MOSFET,導通損耗PD=I2R=0.25W;

若環境溫度85℃,需選RθJC≤(125-85)/0.25=160℃/W的封裝(如TO-263)。

TO-220封裝RθJC≈1.5℃/W,DFN5×6封裝RθJC≈40℃/W,需根據散熱條件選擇。

熱限制:實際電流需≤70% ID(25℃環境溫度下),高溫需降額使用(如125℃時ID降額至50%)。

封裝熱阻(RθJC):

計算示例:

脈沖漏極電流(IDM)

需滿足短路耐受時間(通常1~10μs),可通過SOA(安全工作區)曲線驗證。

3. 導通電阻(RDS(ON)):效率與成本的權衡

溫度系數:RDS(ON)隨溫度升高而增大(典型2~3倍/100℃),需按最高結溫計算:

SiC與Si器件對比:

1200V電壓等級下,SiC MOSFET的RDS(ON)可低至Si器件的1/10(如C3M0075120K vs. IPW65R041CFD7)。

4. 開關參數:動態損耗與EMI的平衡

柵極電荷(QG)

100kHz開關頻率下,QG=100nC的MOSFET需驅動電流≥1A(tON≤100ns)。

直接影響驅動損耗(PDRV=QG×VGS×fSW),需與驅動器能力匹配(如驅動電流≥QG/tON)。

案例:

米勒平臺(VGS(PLAT))

需確保驅動電壓>VGS(PLAT)(通常4~5V),否則開關速度受限。

反向恢復電荷(QRR)

體二極管反向恢復過程產生損耗,需通過軟開關(ZVS/ZCS)或SiC MOSFET(QRR極低)抑制。

5. 封裝與工藝:散熱與布局的協同優化

封裝熱阻對比:

封裝類型 RθJC(℃/W) 典型應用 TO-220 1.5 中低功率(<50W) DFN5×6 40 空間受限設計(如DC-DC模塊) TO-247-4L 0.5 高功率(>100W) PowerPAK 10~20 汽車電子(AEC-Q101認證) 銅夾工藝(Cu Clip):

替代傳統鍵合線,降低封裝電感(LPKG從5nH降至1nH),改善高頻開關性能。

二、應用場景適配:從需求反推選型策略

1. 電源轉換:DC-DC/AC-DC拓撲

Buck/Boost電路:

需低RDS(ON)(如英飛凌OptiMOS系列)以降低導通損耗,同時關注QG(如100kHz下選QG<50nC)。

PFC電路:

需高雪崩能力(EAS>1J)和低COSS(如Wolfspeed Gen3 SiC MOSFET)。

2. 電機驅動:BLDC/PMSM控制

三相逆變器:

需考慮體二極管反向恢復(選SiC MOSFET或超結Si MOSFET),并匹配驅動IC(如DRV8323H)。

死區時間優化:

選QGD/QGS比值小的器件(如QGD/QGS<1.5),減少死區時間導致的轉矩脈動。

3. 汽車電子:高壓/高可靠性

48V系統:

需AEC-Q101認證(如安森美NVHL080N120SC1),并滿足ISO 16750-2振動標準。

電池管理(BMS):

需高精度電流檢測(選RDS(ON)一致性好的器件,如TI CSD19536KTT)。

4. 消費電子:高集成度/低功耗

無線充電:

需超低RDS(ON)(如Alpha & Omega AON7407,RDS(ON)=3.2mΩ@10V)和低柵極電荷。

快充適配器:

需高頻工作(>200kHz)和低COSS(如英飛凌CoolGaN系列)。

三、失效風險規避:選型中的關鍵檢查項

1. 柵極驅動兼容性

驅動電壓范圍:

邏輯電平MOSFET(如VGS(TH)=1~2.5V)需匹配3.3V驅動器(如TXS0108E電平轉換)。

米勒鉗位:

高壓應用需驅動IC內置米勒鉗位(如UCC27712),防止誤導通。

2. 寄生參數影響

封裝電感(LPKG):

高速開關下,LPKG與COSS諧振產生振鈴(EMI問題),需通過RC緩沖電路抑制。

PCB布局:

驅動回路面積需最小化(<1cm2),避免di/dt耦合干擾。

3. 雪崩與短路耐受

雪崩測試:

需通過UIS(非鉗位感性開關)測試(如IEC 60747-9標準),驗證EAS是否達標。

短路保護:

選帶退飽和檢測的驅動IC(如Infineon 1EDI20I12AF),或通過分立電路實現。

四、選型工具與流程:從數據表到實際驗證

1. 參數篩選三步法

電壓/電流邊界:根據供電電壓和負載電流初篩VDSS/ID。

損耗計算:用RDS(ON)和開關損耗(EON+EOFF)評估效率。

熱仿真:通過Flotherm或PLECS驗證結溫是否超標。

2. 供應商推薦(按應用領域)

| 領域 | 推薦廠商 | 代表型號 |

|---|---|---|

| 工業電源 | Infineon、ST、OnSemi | IPW65R041CFD7、STW58N65M5 |

| 汽車電子 | Rohm、NXP、Vishay | BUK7S1R0-40H、SiC464EDY-T1-GE3 |

| SiC器件 | Wolfspeed、ROHM、Infineon | C3M0065090J、SCT30N120 |

| 消費級 | AOS、Nexperia、TI | AON7407、PSMN7R0-30YLDX |

3. 驗證清單

靜態參數(VDSS/ID/RDS(ON))是否滿足規格。

動態參數(QG/tON/tOFF)是否與驅動器匹配。

熱阻與散熱方案是否可行(結溫<150℃)。

EMI是否通過CISPR 32 Class B標準。

極端環境(高溫/高濕/振動)下是否可靠。

五、總結:MOSFET選型的工程化方法論

根本目標:

在電壓/電流安全、效率、成本、EMI的四維約束下,實現零失效、高可靠、易集成的功率電路設計。

技術組合:

器件:Si/SiC MOSFET + 驅動IC + 緩沖電路。

工藝:銅夾封裝 + 3D PCB布局 + 熱仿真優化。

驗證:SOA曲線測試 + 雪崩能量測試 + 加速壽命試驗(HALT)。

工程實踐:

分階段驗證:先參數篩選,再仿真優化,最后實測迭代。

數據驅動:通過損耗(PD)、效率(η)、結溫(TJ)等指標量化評估。

通過系統化選型策略,可實現功率電路效率提升5%~10%、EMI輻射降低20dB、故障率降低80%,為新能源、汽車電子、工業自動化等場景提供高性能功率解決方案。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)