LTC6906微功率精密振蕩器(單片硅振蕩器)在1MHz時僅消耗60μA的辦法

11

11

拍明芯城

拍明芯城

傳統上,電子鐘使用石英晶體,陶瓷諧振器或離散R, L或C元件作為計時參考,但這些設計中的每一種都有幾個缺點,使它們不適合各種應用。石英晶體和陶瓷諧振器可能非常耗電,而且它們的精度受到環境壓力的影響。晶體振蕩器還有一個額外的缺點,就是容易受到沖擊或振動的損害。RC振蕩器抖動和精度差,或者需要昂貴的精密元件。一種更堅固、更緊湊的替代方案是全硅時鐘,如LTC6906微功率電阻控制振蕩器。

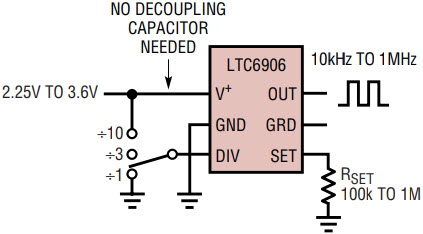

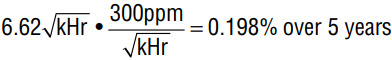

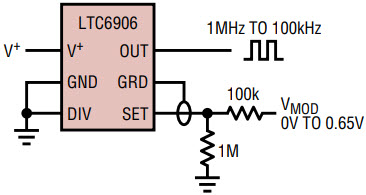

LTC6906是一款單片硅振蕩器,與其他振蕩器相比,具有顯著的尺寸,功率,成本和環境靈敏度優勢,它只需要一個外部電阻就可以將頻率設置在10kHz至1MHz的全范圍內(圖1)。其0.65%的精度和抖動低至0.03%,使其成為精密應用的絕佳選擇,功率和尺寸優勢使LTC6906適合設計晶體振蕩器永遠不會去。

圖1 LTC6906只需要一個外部電阻。

設備描述

LTC6906是Linear Technology的電阻控制SOT-23振蕩器系列的一部分。這些電阻控制振蕩器使用一個便宜的外部電阻來精確地設置振蕩器頻率,并且在電阻值和輸出頻率之間存在簡單的線性關系。

LTC6906采用創新的低功耗架構,主振蕩器運行在100kHz和1MHz之間。提供了一個三狀態分頻引腳,它可以接合一個內部分頻器,將輸出頻率降低1、3或10倍,以提供10kHz至1MHz的總頻率范圍。為了在極低偏置電流下提高頻率范圍下端的精度,為頻率設置電阻輸入提供了保護引腳。

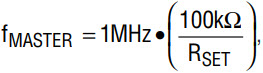

主振蕩器頻率由連接在set引腳和地之間的外部電阻設定。LTC6906將SET引腳維持在離地約650mV,溫度為-2.2mV /°C。主振蕩器頻率與SET電阻的關系如下:

并且只與SET引腳上的電阻有關,而不考慮確切的SET引腳電流或電壓。

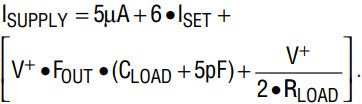

低功耗

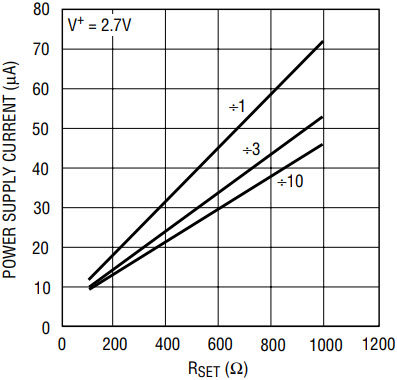

LTC6906運行在100kHz時僅使用10μA(圖2)。該電流消耗有三個組件。內部參考電路和偏置電路使用約5μA的靜態偏置電流。大約6倍于SET電阻器電流的可變偏置電流用于給內部振蕩器供電和偏置。與負載電容、電源電壓和負載電阻有關的負載電流構成了耗散方程的其余部分。總電源電流的近似表達式為:

圖2 LTC6906具有極低的功耗。

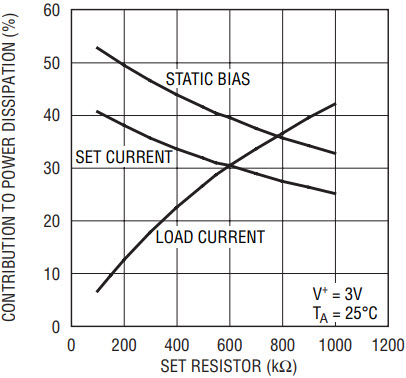

圖3顯示了在負載電容為5pF、無阻性負載的情況下,這三個分量在頻率范圍內的相對幅度。

圖3 靜態偏置、設定電流和負載電流對功耗的貢獻百分比。數據在3V, 25°C環境溫度下采集。

請注意,從100kHz到1MHz工作時,負載中耗散的功率占總功率的25%到40%以上。負載電容或電阻的任何減小都會對電源耗散的負載電流部分產生顯著影響。在100kHz時功耗低至7μA,且光輸出時間較長。降低電源電壓也降低了耗散到負載中的功率。

當負載電流在較高頻率下較高時,嚙合內部分壓器對功耗影響較大,但當內部偏置電流在較低主振蕩器頻率下占主導地位時,影響很小,如圖4所示。

圖4 LTC6906電源電流vs DIV引腳設置。所有數據在3V電源,5pF負載下采集。

選擇SET電阻器

SET電阻器的選擇取決于所需的輸出頻率。該部分指定的主振蕩器頻率在100kHz和1MHz之間,可能的DIV比率為1,3和10。這些DIV范圍重疊,并且一些頻率具有DIV和SET電阻值的多個有效組合。給定頻率的最低功耗總是通過設置盡可能高的SET電阻和盡可能低的DIV來獲得。使用DIV = 10和R(SET) = 100k歐姆產生100kHz比使用DIV = 1和R(SET) = 1000k歐姆消耗更多的功率。

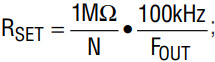

下式將期望的主振蕩器頻率與R(SET)值聯系起來:

其中N是選擇1、3或10的分頻比,R(SET)是SET電阻值,f(OUT)是期望的輸出頻率。例如,在三個DIV設置下生成100kHz輸出頻率的有效R(SET)值參見表1。從表中可以明顯看出,根據DIV引腳的設置,特定輸出頻率的電流可能以高達4.5的因子變化。

選擇最大可能的SET電阻和最小可能的DIV值需要權衡。較小的DIV值會增加抖動,并且由于SET引腳的泄漏,高R(SET)值可能會影響頻率精度,特別是在較高溫度下。

布局的考慮

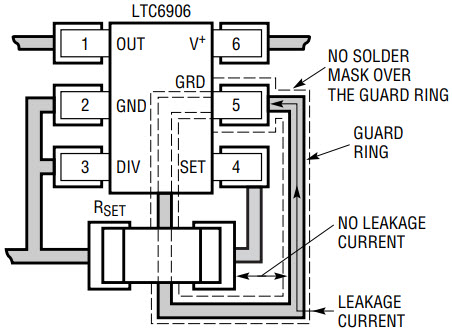

LTC6906在商業溫度范圍內的頻率精度為<0.65%,為了獲得最佳精度,必須注意限制R(SET)引腳周圍的電路板泄漏。對地的1G歐姆寄生電阻可使頻率變化0.1%,對正電源的相同電阻可使頻率變化0.3%。已經提供了一個保護引腳,該保護引腳被弱驅動到與SET引腳相同的直流電壓,并且保護信號應該完全繞SET引腳布線,與設備在PC板的同一側,并且應該沒有焊罩(見圖5)。

圖5 GRD環應與LTC6906在PC板的同一側布線,并應去除阻焊膜。

保護環并非在所有應用中都是必需的,特別是那些具有較低SET電阻值和良好組裝實踐的應用。大多數電路板泄漏問題是由于電路板上的焊劑清洗不夠或裝配草率造成的。完全清潔的組件,保護環是完全不必要的。

LTC6906使用開關電流來驅動SET電阻,因此在SET線上可能會有一些可見的噪聲。雖然這種噪聲不會對輸出信號造成抖動,但在SET引腳上存在寄生電容時,它會影響頻率精度。由于對寄生電容的這種敏感性以及由于長走線產生額外泄漏的危險,建議將SET電阻盡可能靠近SET引腳,并與LTC6906位于PC板的同一側。

硅振蕩器的長期漂移

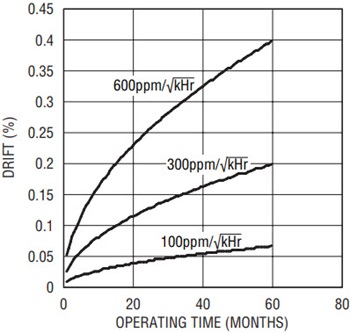

硅振蕩器的長期穩定性以ppm/√為單位指定kHr,這是典型的其他硅器件,如運算放大器和電壓參考。由于硅基振蕩器中的漂移主要是由硅中的離子運動產生的,因此大部分漂移是在器件使用壽命的早期完成的,并且可以預期在長期內漂移會趨于平穩。ppm /√k人力資源單元模型這個時變衰減。晶體振蕩器偶爾指定以ppm/年為單位測量漂移。這種測量模擬了不同的漂移機制,衰減曲線也不相同。圖6顯示了五年期間各種漂移率的比較。

圖6 100ppm/√下5年漂移量的比較kHr, 300 ppm /√kHr600ppm /√kHr.

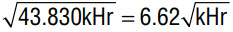

在計算預期漂移量時,重要的是要在計算中考慮整個時間,因為與時間的關系不是線性的。5年的漂移不是1年漂移的5倍。300ppm/√下5年漂移的樣例計算kHr如下:

5年·365.25天/年·24小時/天= 43,830小時= 43.830千瓦時

漂移計算假定部件在整個計算期間處于連續運行狀態。導致漂移的離子運動通常是由操作部件中的電場輔助的,如果在整個漂移期間部件沒有通電,則漂移會大大降低。保守的計算將使用十分之一的漂移規格的時間,當功率不施加到該部分。

切換DIV引腳

LTC6906上的DIV輸入引腳,在許多方面類似于其他LTC硅振蕩器上的DIV引腳,是一個三狀態輸入,能夠解析三種不同的狀態:高,開和低。三態輸入引腳在低引腳數封裝中允許更大的功能,并且與許多微控制器的三態輸出兼容。靜態配置很容易通過將引腳綁到正電源或地,或使其浮動來完成。

在OPEN狀態下,LTC6906的DIV引腳對PC板上常見的噪聲具有一定的抗擾性,但應注意避免引腳上的長浮動走線,或將引腳驅動走線放置在具有強交流信號的線路旁邊。DIV引腳的抗噪性可以通過在地上添加一個電容或在DIV引腳附近放置一個高達100k歐姆的串聯電阻來輕松提高。

正常情況下,DIV引腳會以1μa左右的小電流將DIV引腳電壓拉到電源電壓的一半左右。因此,如果引腳保持打開狀態,引腳上的任何額外電容都會減慢其穩定到open狀態。

使用DIV引腳實時切換頻率的應用需要考慮到這一點,因為它是為低功耗工作設計的,DIV引腳緩沖電路很慢,在DIV引腳激活和LTC6906輸出變化之間的延遲高達12μs左右。在應用中必須考慮到這種開關延遲,或者可以用外部分頻器代替內部分頻器,以減少頻率變化響應時間。

操縱SET引腳

LTC6906可以配置在需要改變SET電阻以在不同頻率下工作的應用中。當改變SET電阻時,將開關機構置于設置電阻和GND之間,而不是設置電阻和SET引腳之間,可以獲得最佳性能和精度(見圖7)。SET引腳對外部電容或信號的干擾很敏感,通過SET電阻進行隔離可以降低這種靈敏度。

圖7 切換不同的SET電阻。

LTC6906并不理想地適合通過SET引腳進行電流調制,因為為了節省功率,SET引腳上的電壓不會隨溫度或負載調節。這導致頻率的調制是設置引腳電壓和設置引腳電流的函數。頻率仍然可以通過SET引腳調制,但調制電流或電壓與輸出頻率之間的關系不是很準確,因為它取決于定義不清的SET引腳電壓。

圖8中的電路顯示了一種調制方法,其結果是低抖動和穩定的性能。通過電阻調制SET引腳電流,減小了寄生電容對初始頻率精度的影響。

圖8 通過電阻調制SET引腳電流可提供更大的抗噪聲耦合能力。

結論

LTC6906是一個微功率振蕩器,精度為0.65%,抖動非常低。其體積小,配置簡單,功耗極低,是驅動微控制器,fpga的低功耗應用的理想選擇,并為電池供電設備提供時鐘參考。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)