74ls27的功能和引腳圖

16

16

拍明芯城

拍明芯城

74LS27三輸入三或非門的功能與引腳圖詳解

一、74LS27芯片概述

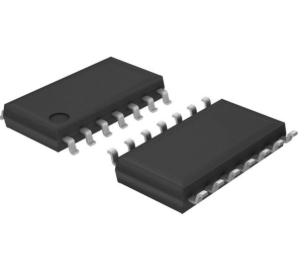

74LS27是一款經(jīng)典的TTL(晶體管-晶體管邏輯)系列數(shù)字集成電路,屬于“低功耗肖特基”(LS)子系列。其核心功能為三輸入三或非門,即內(nèi)部集成三個(gè)獨(dú)立的3輸入或非邏輯單元,每個(gè)單元可對(duì)三個(gè)輸入信號(hào)進(jìn)行或非運(yùn)算,并輸出結(jié)果。該芯片采用雙列直插封裝(DIP),常見為14引腳規(guī)格,因其高速、低功耗和抗干擾能力強(qiáng),廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)、邏輯控制、信號(hào)處理及工業(yè)自動(dòng)化等領(lǐng)域。

二、74LS27的核心功能

1. 或非邏輯運(yùn)算原理

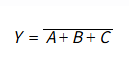

或非門(NOR Gate)是基本邏輯門之一,其輸出為“1”的條件是所有輸入均為“0”,否則輸出為“0”**。對(duì)于三輸入或非門,邏輯表達(dá)式為:

即僅當(dāng)輸入A、B、C全為低電平時(shí),輸出Y為高電平;任一輸入為高電平,輸出即變?yōu)榈碗娖健?4LS27內(nèi)部集成了三個(gè)這樣的邏輯單元,可獨(dú)立處理三組信號(hào)。

2. 電氣特性與參數(shù)

電源電壓:工作范圍為4.75V至5.25V,典型值為5V,兼容TTL標(biāo)準(zhǔn)電平。

輸入/輸出電流:

輸入低電平電流(IIL):最大-0.4mA(吸收電流)。

輸出低電平電流(IOL):最大8mA(驅(qū)動(dòng)能力)。

輸出高電平電流(IOH):最大-0.4mA(灌電流能力)。

傳播延遲:典型值為10ns(高電平到低電平)和10ns(低電平到高電平),支持最高35Mbps的數(shù)據(jù)傳輸速率。

功耗:靜態(tài)功耗約13.5mW,遠(yuǎn)低于早期TTL芯片,適合低功耗設(shè)計(jì)。

3. 典型應(yīng)用場景

邏輯控制:用于設(shè)計(jì)復(fù)雜的條件判斷電路,如工業(yè)設(shè)備的啟動(dòng)/停止控制。

信號(hào)編碼與解碼:在通信系統(tǒng)中實(shí)現(xiàn)多路信號(hào)的合并或分離。

狀態(tài)機(jī)設(shè)計(jì):作為組合邏輯部分,參與時(shí)序電路的狀態(tài)轉(zhuǎn)換。

接口電路:實(shí)現(xiàn)不同電平標(biāo)準(zhǔn)之間的邏輯轉(zhuǎn)換或緩沖。

三、74LS27引腳圖與功能分配

1. 引腳圖詳解

74LS27采用14引腳DIP封裝,其引腳排列及功能如下:

| 引腳編號(hào) | 符號(hào) | 功能描述 | 輸入/輸出 | 邏輯單元關(guān)聯(lián) |

|---|---|---|---|---|

| 1 | 1A | 第一邏輯單元輸入A | 輸入 | 單元1 |

| 2 | 1B | 第一邏輯單元輸入B | 輸入 | 單元1 |

| 3 | 1C | 第一邏輯單元輸入C | 輸入 | 單元1 |

| 4 | 1Y | 第一邏輯單元輸出 | 輸出 | 單元1 |

| 5 | 2A | 第二邏輯單元輸入A | 輸入 | 單元2 |

| 6 | 2B | 第二邏輯單元輸入B | 輸入 | 單元2 |

| 7 | GND | 電源地 | 電源 | - |

| 8 | 3C | 第三邏輯單元輸入C | 輸入 | 單元3 |

| 9 | 3B | 第三邏輯單元輸入B | 輸入 | 單元3 |

| 10 | 3A | 第三邏輯單元輸入A | 輸入 | 單元3 |

| 11 | 3Y | 第三邏輯單元輸出 | 輸出 | 單元3 |

| 12 | 2Y | 第二邏輯單元輸出 | 輸出 | 單元2 |

| 13 | 2C | 第二邏輯單元輸入C | 輸入 | 單元2 |

| 14 | VCC | 電源正極(+5V) | 電源 | - |

2. 引腳功能說明

輸入引腳(1A-3C):每個(gè)邏輯單元有三個(gè)輸入端,共九個(gè)輸入引腳,用于接收外部信號(hào)。

輸出引腳(1Y-3Y):對(duì)應(yīng)三個(gè)邏輯單元的輸出端,輸出或非運(yùn)算結(jié)果。

電源引腳(VCC、GND):提供芯片工作所需的直流電源,VCC接+5V,GND接地。

3. 引腳連接注意事項(xiàng)

未使用引腳處理:未使用的輸入引腳應(yīng)通過上拉電阻接至VCC(高電平)或下拉至GND(低電平),避免懸空導(dǎo)致邏輯狀態(tài)不確定。

輸出負(fù)載能力:單個(gè)輸出引腳的最大驅(qū)動(dòng)電流為8mA,總功耗不超過芯片額定值,避免過載。

信號(hào)完整性:長距離傳輸時(shí),輸出端可串聯(lián)小電阻(如22Ω)抑制振蕩,輸入端可并聯(lián)0.1μF電容濾波。

四、74LS27的邏輯功能驗(yàn)證

1. 真值表分析

以第一邏輯單元為例,其真值表如下:

| A | B | C | Y = ?(A+B+C) |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

從真值表可見,僅當(dāng)A、B、C全為0時(shí),輸出Y為1;其他情況輸出均為0。

2. 實(shí)驗(yàn)驗(yàn)證方法

測試電路搭建:

將74LS27的VCC接+5V,GND接地。

通過撥碼開關(guān)控制輸入引腳(1A-1C)的電平,LED指示燈連接輸出引腳(1Y)。

觀察LED狀態(tài),驗(yàn)證邏輯功能。

預(yù)期結(jié)果:

當(dāng)所有撥碼開關(guān)置于“0”(接地)時(shí),LED亮起(輸出1)。

任一開關(guān)置于“1”(接VCC)時(shí),LED熄滅(輸出0)。

3. 常見問題排查

輸出異常:檢查電源電壓是否穩(wěn)定,輸入引腳是否懸空或接觸不良。

過熱現(xiàn)象:可能是負(fù)載過大或短路,需檢查輸出驅(qū)動(dòng)電流是否超限。

時(shí)序問題:在高頻率應(yīng)用中,需考慮傳播延遲對(duì)信號(hào)同步的影響。

五、74LS27的擴(kuò)展應(yīng)用與優(yōu)化設(shè)計(jì)

1. 多級(jí)邏輯組合

通過級(jí)聯(lián)多個(gè)74LS27芯片,可實(shí)現(xiàn)更復(fù)雜的邏輯功能。例如:

四輸入或非門:將兩個(gè)3輸入或非門的輸出通過一個(gè)與門組合,可等效為四輸入或非門。

奇偶校驗(yàn)電路:利用或非門實(shí)現(xiàn)多位數(shù)據(jù)的奇偶性檢測。

2. 與其他芯片的協(xié)同設(shè)計(jì)

與74LS00(與非門)結(jié)合:通過或非門與非門的組合,可實(shí)現(xiàn)任意布爾函數(shù)。

與觸發(fā)器配合:在時(shí)序電路中,或非門的輸出可作為觸發(fā)器的時(shí)鐘或復(fù)位信號(hào)。

3. 低功耗優(yōu)化技巧

降低電源電壓:在允許范圍內(nèi)適當(dāng)降低VCC(如4.75V),可減少功耗。

減少輸出負(fù)載:通過增加緩沖器(如74LS244)驅(qū)動(dòng)大負(fù)載,避免直接連接高容性負(fù)載。

啟用休眠模式:若芯片支持,可在空閑時(shí)關(guān)閉部分邏輯單元以降低功耗。

六、74LS27的替代方案與選型建議

1. 替代芯片對(duì)比

74HC27:CMOS工藝版本,工作電壓范圍更寬(2V至6V),功耗更低,但速度略慢于74LS27。

74HCT27:兼容TTL電平的CMOS芯片,適合混合電壓系統(tǒng)。

CD4025:三輸入或非門,CMOS工藝,工作電壓3V至15V,適合低速、寬電壓應(yīng)用。

2. 選型依據(jù)

速度要求:高速應(yīng)用優(yōu)先選74LS27,低速應(yīng)用可選74HC27或CD4025。

功耗敏感場景:推薦74HC27或74HCT27。

成本因素:74LS27價(jià)格適中,適合大批量生產(chǎn);CMOS版本單價(jià)可能略高。

七、74LS27的封裝與可靠性設(shè)計(jì)

1. 封裝類型與散熱

DIP封裝:適合手工焊接與原型開發(fā),但體積較大,散熱能力有限。

SOP封裝:部分廠商提供SOP-14版本,體積更小,適合高密度PCB設(shè)計(jì)。

散熱建議:在高溫環(huán)境下,可通過增加PCB銅箔面積或安裝散熱片改善散熱。

2. 可靠性設(shè)計(jì)要點(diǎn)

電源去耦:在VCC引腳附近并聯(lián)0.1μF陶瓷電容,抑制高頻噪聲。

ESD防護(hù):輸入/輸出引腳增加TVS二極管,防止靜電擊穿。

熱設(shè)計(jì):避免芯片長期工作在最大結(jié)溫(125℃)以上,確保環(huán)境溫度低于70℃。

八、74LS27的行業(yè)應(yīng)用案例

1. 工業(yè)自動(dòng)化控制

在某生產(chǎn)線中,74LS27用于實(shí)現(xiàn)多傳感器信號(hào)的邏輯判斷。例如:

輸入A:溫度傳感器信號(hào)(正常時(shí)為0,超溫時(shí)為1)。

輸入B:壓力傳感器信號(hào)(正常時(shí)為0,超壓時(shí)為1)。

輸入C:安全門狀態(tài)信號(hào)(關(guān)閉時(shí)為0,開啟時(shí)為1)。

輸出Y:控制電機(jī)停機(jī)(僅當(dāng)所有信號(hào)正常時(shí)Y=1,允許運(yùn)行)。

2. 數(shù)字時(shí)鐘設(shè)計(jì)

在簡易數(shù)字時(shí)鐘中,74LS27用于實(shí)現(xiàn)分頻與邏輯控制:

輸入信號(hào):來自晶振的分頻脈沖。

邏輯功能:通過或非門組合實(shí)現(xiàn)秒、分、時(shí)的進(jìn)位控制。

輸出信號(hào):驅(qū)動(dòng)數(shù)碼管顯示或蜂鳴器報(bào)時(shí)。

3. 通信接口電路

在RS-232轉(zhuǎn)TTL電平轉(zhuǎn)換電路中,74LS27用于信號(hào)緩沖與電平匹配:

輸入:RS-232接收端信號(hào)(±12V電平,經(jīng)電平轉(zhuǎn)換后為TTL電平)。

輸出:經(jīng)過或非門緩沖的TTL信號(hào),供MCU處理。

九、74LS27的未來發(fā)展趨勢

1. 技術(shù)演進(jìn)方向

更低功耗:隨著CMOS工藝進(jìn)步,未來或非門芯片的靜態(tài)功耗將進(jìn)一步降低。

更高集成度:將多個(gè)邏輯門集成到更小封裝中,如QFN或BGA。

智能化:結(jié)合可編程邏輯(如CPLD),實(shí)現(xiàn)動(dòng)態(tài)配置的或非門功能。

2. 市場前景分析

傳統(tǒng)市場:工業(yè)控制、儀器儀表等領(lǐng)域?qū)?4LS27的需求將保持穩(wěn)定。

新興領(lǐng)域:物聯(lián)網(wǎng)、智能家居等場景中,低功耗或非門芯片將用于傳感器信號(hào)處理。

十、總結(jié)

74LS27作為一款經(jīng)典的三輸入三或非門芯片,憑借其高速、低功耗和可靠的邏輯功能,在數(shù)字電路設(shè)計(jì)中占據(jù)重要地位。本文從芯片概述、功能原理、引腳圖解析、應(yīng)用驗(yàn)證到選型建議,全面闡述了74LS27的核心特性與設(shè)計(jì)要點(diǎn)。無論是初學(xué)者學(xué)習(xí)數(shù)字邏輯,還是工程師開發(fā)實(shí)際項(xiàng)目,掌握74LS27的使用方法均具有重要意義。未來,隨著技術(shù)不斷進(jìn)步,74LS27及其衍生芯片將在更多領(lǐng)域發(fā)揮關(guān)鍵作用,推動(dòng)數(shù)字電路設(shè)計(jì)向更高性能、更低功耗的方向發(fā)展。

責(zé)任編輯:David

【免責(zé)聲明】

1、本文內(nèi)容、數(shù)據(jù)、圖表等來源于網(wǎng)絡(luò)引用或其他公開資料,版權(quán)歸屬原作者、原發(fā)表出處。若版權(quán)所有方對(duì)本文的引用持有異議,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com),本方將及時(shí)處理。

2、本文的引用僅供讀者交流學(xué)習(xí)使用,不涉及商業(yè)目的。

3、本文內(nèi)容僅代表作者觀點(diǎn),拍明芯城不對(duì)內(nèi)容的準(zhǔn)確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨(dú)立判斷做出的,請(qǐng)讀者明確相關(guān)結(jié)果。

4、如需轉(zhuǎn)載本方擁有版權(quán)的文章,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com)注明“轉(zhuǎn)載原因”。未經(jīng)允許私自轉(zhuǎn)載拍明芯城將保留追究其法律責(zé)任的權(quán)利。

拍明芯城擁有對(duì)此聲明的最終解釋權(quán)。

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)