什么是gd25q256,gd25q256的基礎知識?

1

1

拍明芯城

拍明芯城

GD25Q256 NOR 閃存基礎知識

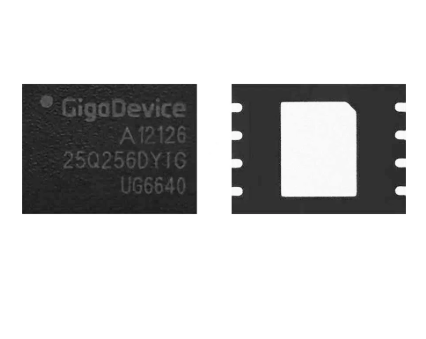

GD25Q256 是一款由兆易創新(GigaDevice)生產的 NOR 型串行閃存芯片。它在嵌入式系統、消費電子、工業控制和物聯網設備等領域有著廣泛的應用。由于其非易失性、高性能和低功耗特性,GD25Q256 成為了許多設計工程師首選的存儲解決方案。

NOR 閃存概述

在深入探討 GD25Q256 之前,理解 NOR 閃存的基本原理至關重要。NOR 閃存是一種非易失性存儲器,這意味著即使斷電,它也能保持存儲的數據。其名稱來源于其內部存儲單元的“非或(NOT OR)”門結構。與 NAND 閃存不同,NOR 閃存允許隨機訪問每個字節,這使得它非常適合存儲需要頻繁讀取且隨機訪問的程序代碼和配置文件。

NOR 閃存的優點包括:

隨機讀取能力: 可以像 RAM 一樣直接執行代碼,無需先將代碼載入 RAM,這被稱為“就地執行”(Execute In Place, XIP)。

高可靠性: 通常比 NAND 閃存具有更高的擦寫壽命和數據保留能力。

易于接口: 通常采用簡單的串行外設接口(SPI),易于與微控制器和處理器連接。

然而,NOR 閃存也有一些缺點:

寫入速度較慢: 相比 NAND 閃存,寫入和擦除操作通常較慢。

成本較高: 單位存儲容量的成本通常高于 NAND 閃存。

存儲密度較低: 通常適用于中小容量的存儲需求。

GD25Q256 的核心特性

GD25Q256 作為一款典型的 NOR 閃存芯片,具備許多關鍵特性,使其在市場中脫穎而出。

存儲容量: GD25Q256 的型號名稱中的“256”表示其存儲容量為 256 兆位(Megabit),即 32 兆字節(Megabyte)。這種容量對于存儲嵌入式系統的操作系統、固件、啟動代碼和少量應用數據來說通常是足夠的。隨著設備功能的日益復雜,更高的存儲容量需求也在增長,但 32MB 對于許多傳統和新興應用仍具有重要意義。

接口類型: GD25Q256 主要通過 串行外設接口(SPI) 進行通信。SPI 是一種同步串行數據總線標準,由摩托羅拉公司開發,用于短距離、主從模式通信。SPI 接口具有以下優點:

引腳數量少: 通常只需要四根線(片選CS、時鐘SCK、主輸出從輸入MOSI、主輸入從輸出MISO),這有助于簡化 PCB 設計并降低成本。

全雙工通信: 數據可以同時發送和接收。

高速率: GD25Q256 支持高達 120MHz 的時鐘頻率,使得數據傳輸速率非常高,這對于需要快速啟動和數據訪問的系統至關重要。

四路 SPI(Quad SPI): 除了標準的單路 SPI 模式,GD25Q256 還支持雙路 SPI(Dual SPI)和四路 SPI(Quad SPI)模式。四路 SPI 模式通過使用更多的I/O引腳并行傳輸數據,極大地提高了吞吐量,尤其是在讀取大量數據時,可以顯著縮短等待時間,提升系統整體性能。例如,在代碼就地執行(XIP)應用中,更高的讀取速度意味著更快的程序執行。

電源電壓: GD25Q256 通常工作在 2.7V 至 3.6V 的寬電壓范圍,這使得它能夠與大多數微控制器和處理器兼容。低電壓操作也有助于降低整體功耗,這對于電池供電的設備尤為重要。

擦寫壽命: NOR 閃存的一個關鍵指標是其擦寫循環次數。GD25Q256 通常支持 10 萬次以上的擦寫循環。這意味著每個存儲塊可以被擦除和編程至少 10 萬次,這對于存儲固件等不經常更新的數據來說綽綽有余。對于需要頻繁寫入的應用,如日志記錄,設計者需要考慮使用磨損均衡算法來延長閃存壽命。

數據保留能力: GD25Q256 保證數據在非通電狀態下可以保留 20 年以上。這一特性對于長期存儲關鍵數據至關重要,確保即使設備長時間不通電,其內部的固件和配置信息也不會丟失。

安全性特性: 考慮到嵌入式設備的安全性日益重要,GD25Q256 通常集成了多種安全特性。這包括:

OTP(一次性可編程)內存: 通常用于存儲唯一的設備ID、序列號或加密密鑰,一旦編程就無法更改,增加了設備的安全性。

寫保護功能: 可以通過軟件或硬件方式對特定區域進行寫保護,防止未經授權的修改或意外擦除關鍵數據。例如,可以保護啟動代碼區域,確保系統啟動的完整性。

JEDEC 標準兼容: GD25Q256 遵循 JEDEC(聯合電子器件工程委員會)的通用閃存標準,這意味著它的命令集和操作方式與其他符合 JEDEC 標準的閃存芯片兼容,方便工程師在不同供應商的芯片之間進行切換。

GD25Q256 的內部結構

理解 GD25Q256 的內部結構有助于更好地利用其功能。GD25Q256 通常被組織成幾個邏輯區域:

主存儲區: 這是最主要的存儲區域,用于存儲代碼和數據。它被劃分為若干個扇區(Sector)和塊(Block)。

扇區(Sector): 通常是可擦除的最小單元,GD25Q256 的扇區大小通常為 4KB。擦除操作會清除整個扇區的數據。

塊(Block): 由多個扇區組成,通常是更大的擦除單元,例如 32KB 或 64KB。塊擦除操作比扇區擦除更快,但擦除的顆粒度更大。

狀態寄存器(Status Register): 存儲閃存的當前狀態信息,例如寫操作是否正在進行、擦除是否完成、寫保護狀態等。通過讀取狀態寄存器,微控制器可以了解閃存的工作情況。

配置寄存器(Configuration Register): 允許用戶配置閃存的各種工作模式和參數,例如 SPI 模式、驅動強度等。

安全寄存器(Security Register)/OTP 區域: 包含 OTP 內存和一些安全相關的控制位。

GD25Q256 的基本操作

對 GD25Q256 的操作主要包括讀取、寫入、擦除和設備管理。所有這些操作都通過發送特定的命令字節給芯片來完成。

讀取操作:

普通讀取: 這是最基本的讀取方式,通過發送讀取命令和地址來獲取數據。

快速讀取: 相比普通讀取,快速讀取在命令后會增加一個空周期(dummy cycle),允許芯片有更多時間準備數據,從而實現更高的讀取速度。

雙路/四路 SPI 讀取: 在雙路或四路模式下,數據傳輸速度成倍增長,顯著提升了讀取性能。

寫入操作(編程):

寫入操作通常以字節或頁(Page)為單位進行。頁是可編程的最小單元,GD25Q256 的頁大小通常為 256 字節。

在寫入數據之前,需要先將目標區域進行擦除。不能直接覆蓋已有的數據,因為閃存的編程原理是使存儲單元從“1”變為“0”。如果需要將“0”變為“1”,則必須進行擦除操作。

寫入過程通常需要先發送寫使能命令(Write Enable),然后發送編程命令和數據。

擦除操作:

扇區擦除: 清除 4KB 扇區內的所有數據,將所有位設置為“1”。

塊擦除: 清除 32KB 或 64KB 塊內的所有數據。

芯片擦除: 清除整個閃存芯片的所有數據。這是最耗時的擦除操作。

設備管理操作:

讀狀態寄存器: 獲取閃存的當前狀態。

寫狀態寄存器: 配置閃存的寫保護等功能。

讀設備 ID: 獲取芯片的制造商 ID 和設備 ID,用于識別芯片型號。

進入/退出深度掉電模式: 降低功耗,延長電池壽命。

軟件復位: 通過軟件命令使芯片復位。

GD25Q256 的應用場景

GD25Q256 NOR 閃存在各種電子產品中扮演著關鍵角色,主要應用場景包括:

嵌入式系統: 廣泛用于存儲微控制器或微處理器中的固件(firmware),如 BIOS/UEFI、啟動加載程序(bootloader)和操作系統內核。其 XIP 能力使得系統可以快速啟動,無需將代碼復制到 RAM。

消費電子產品: 例如智能電視、機頂盒、DVD/藍光播放器、打印機、智能家居設備等。GD25Q256 用于存儲這些設備的操作系統、用戶界面、配置文件和升級固件。

工業控制: 在工業自動化設備、機器人、人機界面(HMI)中,GD25Q256 存儲控制程序、配置參數和日志數據,確保設備穩定可靠運行。

網絡通信設備: 路由器、交換機、調制解調器等設備使用 NOR 閃存存儲網絡操作系統、路由表和設備配置。

汽車電子: 在汽車信息娛樂系統、儀表盤、車身控制單元中,GD25Q256 用于存儲啟動代碼、診斷程序和配置數據。

物聯網(IoT)設備: 智能傳感器、智能網關、可穿戴設備等小型化、低功耗的物聯網設備常采用 GD25Q256 存儲其輕量級操作系統、應用代碼和網絡連接參數。

醫療設備: 存儲醫療儀器的固件、校準數據和診斷程序,確保設備的準確性和可靠性。

GD25Q256 的選型考量

在選擇 GD25Q256 或其他 NOR 閃存芯片時,工程師需要考慮以下幾個關鍵因素:

容量需求: 根據應用所需的存儲空間確定閃存容量。如果存儲的固件較大或需要存儲大量數據,可能需要更大容量的芯片。

性能要求: 考量讀取速度、寫入速度和擦除速度。對于需要快速啟動或頻繁讀取代碼的應用,選擇支持高速 SPI 或 Quad SPI 的芯片至關重要。

功耗: 對于電池供電或對功耗敏感的應用,需要關注芯片的靜態電流和工作電流,以及是否支持深度掉電模式。

接口兼容性: 確保閃存芯片的接口類型(如 SPI)和電壓范圍與主控芯片兼容。

可靠性: 關注擦寫壽命和數據保留能力,確保芯片能夠滿足產品的長期使用需求。

成本: 在滿足性能和可靠性要求的前提下,選擇性價比最高的芯片。

封裝類型: 常見的封裝包括 SOIC(小外形集成電路)、WSON(超薄小外形無引線封裝)、USON(超小外形無引線封裝)等,根據 PCB 空間和生產工藝選擇合適的封裝。

供應商支持: 選擇有良好技術支持和穩定供貨能力的供應商,如兆易創新。

GD25Q256 的編程與擦除機制

深入理解 GD25Q256 的編程和擦除機制有助于優化系統設計和提高閃存的壽命。

編程原理: NOR 閃存的存儲單元是浮柵晶體管。編程過程通過在高電壓下將電子注入浮柵,從而改變晶體管的導通狀態,進而表示“0”或“1”。一旦電子被注入,它們會被困在浮柵中,即使斷電也能保持狀態,這就是非易失性的來源。由于編程操作只能將位從“1”變為“0”(通過注入電子),因此在將一個位從“0”變為“1”之前,必須先將整個扇區或塊擦除,使其所有位都變為“1”。

頁編程: GD25Q256 通常以頁為單位進行編程,頁大小為 256 字節。微控制器會發送編程命令、地址和要寫入的數據。芯片內部的編程算法會負責將數據寫入到指定的頁。

擦除原理: 擦除操作是將被編程的浮柵中的電子通過高電壓場強抽出,使所有存儲單元回到“1”的狀態。擦除操作通常是整個扇區或塊進行,無法擦除單個字節。

擦寫壽命與磨損均衡: 閃存的擦寫壽命是有限的。每次擦除操作都會對存儲單元造成一定的物理損傷。為了延長閃存的整體壽命,尤其是在頻繁寫入的應用中,需要采用 磨損均衡(Wear Leveling) 算法。磨損均衡算法的目的是將擦寫操作平均分配到閃存的不同存儲塊上,避免某些塊被過度擦寫而提前失效。這可以通過軟件在文件系統層實現,或者通過閃存控制器硬件實現。例如,當一個文件需要更新時,不是在原位置直接更新,而是將新數據寫入一個未被擦寫過的塊,并將舊塊標記為無效。

GD25Q256 的可靠性與數據完整性

數據完整性對于許多應用至關重要,GD25Q256 采取了多種措施來確保數據的可靠存儲。

ECC(錯誤校驗碼): 某些高端 NOR 閃存可能集成 ECC 功能,但在 GD25Q256 這樣的通用串行閃存中,通常不內置硬件 ECC。如果需要 ECC,通常由主控制器在軟件層面實現。ECC 通過在數據中添加冗余位來檢測和糾正錯誤,從而提高數據的可靠性。

壞塊管理: NOR 閃存通常在出廠時就保證沒有壞塊,或者只有極少數壞塊。然而,隨著使用時間的增長,閃存可能會出現壞塊。良好的文件系統或閃存驅動程序應該具備壞塊管理能力,能夠識別并跳過壞塊,從而確保存儲數據的完整性。

掉電保護: GD25Q256 具備良好的掉電保護機制。在正常工作時,如果突然斷電,正在進行的寫入或擦除操作可能會不完整。為了防止數據損壞,GD25Q256 通常會提供保護機制,例如在寫入操作完成前將數據緩存,或者在檢測到掉電時迅速完成當前操作。

溫度特性: GD25Q256 通常支持工業級溫度范圍(-40°C 至 +85°C),甚至更寬的汽車級溫度范圍,這使得它能夠在惡劣的環境下穩定工作。溫度對閃存的性能和壽命都有影響,極端溫度可能會加速閃存老化。

GD25Q256 的接口與通信協議

GD25Q256 主要通過 SPI 接口進行通信,理解 SPI 協議對于正確使用芯片至關重要。

SPI 總線結構: SPI 總線通常由以下四根線組成:

SCLK(Serial Clock): 串行時鐘線,由主設備生成,用于同步數據傳輸。

CS/SS(Chip Select/Slave Select): 片選線,由主設備控制,用于選擇哪個從設備進行通信。低電平有效。

MOSI(Master Out Slave In): 主設備數據輸出,從設備數據輸入。

MISO(Master In Slave Out): 主設備數據輸入,從設備數據輸出。

SPI 工作模式: SPI 有四種工作模式(Mode 0, 1, 2, 3),通過時鐘極性(CPOL)和時鐘相位(CPHA)來定義。GD25Q256 通常支持其中的一種或多種模式。

命令與數據傳輸: 與 GD25Q256 的通信是通過發送一系列命令字節來實現的。每個命令后面可能跟著地址字節、空周期字節和數據字節。例如,讀取操作通常是:片選拉低 -> 發送讀取命令 -> 發送地址 -> 接收數據 -> 片選拉高。

Quad SPI 協議: 為了提高吞吐量,GD25Q256 支持 Quad SPI。在 Quad SPI 模式下,MOSI 和 MISO 線不再是單向數據線,而是變成雙向的 I/O 線(IO0 和 IO1),并新增了 IO2 和 IO3 兩根數據線。這樣,每次時鐘脈沖可以傳輸 4 位數據,使得數據傳輸速率比單路 SPI 快 4 倍。在 Quad SPI 讀取數據時,通常會有一個特定的命令和地址階段,然后進入數據傳輸階段,數據通過四根線并行傳輸。

GD25Q256 的軟件驅動與固件開發

在實際應用中,與 GD25Q256 交互需要編寫相應的軟件驅動。

底層驅動: 這部分驅動直接與微控制器的 SPI 外設交互,負責發送和接收數據,控制片選線,以及配置 SPI 時鐘頻率和模式。

閃存抽象層: 在底層驅動之上,通常會有一個閃存抽象層,它提供了一系列高層 API,如

flash_read(address, buffer, size)、flash_write(address, buffer, size)、flash_erase_sector(sector_address)等。這些 API 隱藏了底層 SPI 通信的復雜性,使上層應用開發更加便捷。文件系統: 對于需要管理多個文件或動態數據的應用,可以在閃存之上運行一個輕量級的文件系統,如 LittleFS、FatFs 或 JFFS2 等。這些文件系統負責管理文件的創建、刪除、讀取、寫入,并處理磨損均衡和壞塊管理,從而延長閃存壽命。

固件更新: GD25Q256 在固件更新(Firmware Over-The-Air, FOTA 或 OTA)中扮演重要角色。通常,固件更新會涉及將新的固件鏡像下載到閃存的某個備份區域,然后系統在下次啟動時切換到新固件。這種機制需要閃存具有足夠的容量來存儲兩個固件副本(或一個主副本和一個備份副本),并需要安全的引導加載程序來管理固件切換和回滾。

GD25Q256 的發展趨勢

隨著技術的發展,NOR 閃存芯片也在不斷進步。

更高密度: 雖然 NAND 閃存主導了大容量存儲市場,但 NOR 閃存也在向更高密度發展,以滿足更復雜的嵌入式系統需求。

更快速度: 隨著系統時鐘頻率的提高,NOR 閃存的讀取速度也在不斷提升,例如支持更高頻率的 Quad SPI 或其他并行接口。

更低功耗: 對于物聯網和可穿戴設備,低功耗是永恒的追求,未來的 NOR 閃存將繼續優化功耗表現。

集成度更高: 可能會與微控制器或其他功能集成,形成更緊湊的系統級封裝(System-in-Package, SiP)解決方案。

更強安全性: 隨著網絡攻擊的日益復雜,閃存芯片將集成更強大的硬件安全特性,例如硬件加密引擎、安全啟動支持等,以保護代碼和數據的完整性和機密性。

總結

GD25Q256 作為一款典型的 NOR 串行閃存芯片,以其非易失性、隨機讀取能力、SPI 接口易用性和高可靠性,在各種嵌入式和消費電子產品中發揮著不可替代的作用。從基本的容量、接口、電壓特性到復雜的編程、擦除機制和應用場景,GD25Q256 的每一個方面都體現了其作為關鍵存儲組件的價值。理解這些基礎知識不僅有助于工程師正確選擇和使用該芯片,更能為其在日益復雜的電子設計中發揮最大效能奠定基礎。隨著技術的進步,NOR 閃存將繼續演進,以滿足未來電子設備對存儲更高性能、更低功耗和更強安全性的需求。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)