一、概述

74LS153 是屬于 TTL 邏輯家族中的雙 4 選 1 多路復(fù)用器芯片,全稱 SN74LS153,由兩組獨(dú)立的四路數(shù)據(jù)輸入、雙路使能控制以及兩組地址選擇線路組成。每個(gè)多路復(fù)用器可通過兩位地址輸入(A0、A1)在四條數(shù)據(jù)信號(hào)線中選擇一路輸出,同時(shí)具有單獨(dú)的使能端(G),可對(duì)整個(gè)模塊的輸出進(jìn)行整體使能或禁止。74LS153 采用 LS(低功耗肖特基)工藝制造,具有比標(biāo)準(zhǔn) TTL 更低的功耗、更快的切換速度以及更好的抗噪性能,因此在數(shù)字電路中被廣泛用于信號(hào)路由、數(shù)據(jù)選通以及組合邏輯實(shí)現(xiàn)等場(chǎng)合。該芯片封裝形式通常為 16 引腳的雙列直插(DIP-16)或小型封裝(SOP-16),供電電壓 VCC 為 +5V,工作電流典型值約為 10~20mA,輸出為 TTL 電平,同時(shí)輸入允許較寬的共模電壓范圍,可兼容多種邏輯電平接口。

二、封裝與外觀

74LS153 封裝體積適中,典型的 DIP-16 塑封封裝外形尺寸約為 長 20mm、寬 7.5mm、高 3.3mm,引腳間距標(biāo)準(zhǔn)為 2.54mm,使其可直接插入面包板或標(biāo)準(zhǔn) PCB 孔徑。芯片正面通常印有“74LS153”字樣及生產(chǎn)批次號(hào),背面平坦無標(biāo)識(shí)。SOP-16 封裝尺寸更小,適用于空間受限的表貼電路設(shè)計(jì)。無論何種封裝,均在頂視圖時(shí)從左上角開始按逆時(shí)針方向編號(hào),編號(hào)規(guī)則與否則從 G1、A1、B1 等標(biāo)記可幫助快速定位各引腳功能。由于 LS 系列工藝對(duì)散熱不敏感,封裝底部無散熱片,但在高密度電路板上仍需注意布局時(shí)避免熱源積聚。

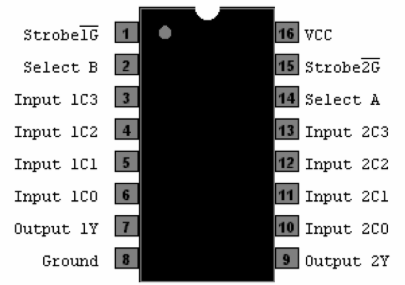

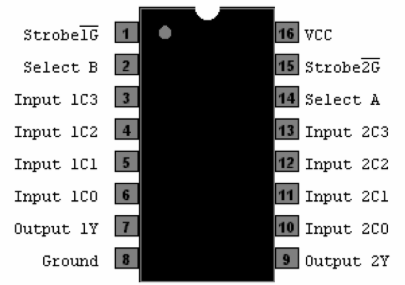

三、引腳圖

以下為 74LS153 在 DIP-16 封裝下的引腳排列示意(頂視圖,左上角為引腳 1):

具體對(duì)應(yīng)關(guān)系如下

引腳 1:G1(使能輸入 1)

引腳 2:A1(地址選擇 1 的低位)

引腳 3:B1(地址選擇 1 的高位)

引腳 4:1C0(第一組數(shù)據(jù)輸入 0)

引腳 5:1C1(第一組數(shù)據(jù)輸入 1)

引腳 6:1C2(第一組數(shù)據(jù)輸入 2)

引腳 7:1C3(第一組數(shù)據(jù)輸入 3)

引腳 8:GND(地,邏輯 0 參考電位)

引腳 9:2C3(第二組數(shù)據(jù)輸入 3)

引腳 10:2C2(第二組數(shù)據(jù)輸入 2)

引腳 11:2C1(第二組數(shù)據(jù)輸入 1)

引腳 12:2C0(第二組數(shù)據(jù)輸入 0)

引腳 13:B2(地址選擇 2 的高位)

引腳 14:A2(地址選擇 2 的低位)

引腳 15:G2(使能輸入 2)

引腳 16:VCC(+5V 電源正極)

四、引腳功能表

列表標(biāo)題

? G1、G2(使能輸入)

? A1、B1、A2、B2(地址選擇)

? 1C0~1C3、2C0~2C3(數(shù)據(jù)輸入)

? 1Y、2Y(數(shù)據(jù)輸出)

? VCC、GND(電源與地)

引腳功能詳解

G1 和 G2 均為低電平有效的使能輸入,當(dāng)相應(yīng)的 G 引腳為“0”電平時(shí),對(duì)應(yīng)通道才允許 A、B 地址與 C 數(shù)據(jù)線聯(lián)動(dòng),輸出 Y;若 G=“1”則輸出被強(qiáng)制置為高阻狀態(tài),可實(shí)現(xiàn)總線隔離或輸出凍結(jié)功能,非常適合多路總線共享場(chǎng)景。

地址選擇引腳 A1、B1 和 A2、B2 的組合分別對(duì)應(yīng)多路復(fù)用器的 00、01、10、11 四個(gè)狀態(tài),對(duì)應(yīng)選擇 C0、C1、C2、C3 四路輸入之一。需要注意地址引腳在電平切換時(shí)若存在毛刺或抖動(dòng),可能導(dǎo)致輸出短暫錯(cuò)誤,因此在高速切換應(yīng)用中可通過 RC 濾波或加緩沖門電路消除毛刺。

數(shù)據(jù)輸入引腳 1C0~1C3 及 2C0~2C3 分別對(duì)應(yīng)兩組通道的四路待選信號(hào),允許 TTL 兼容電平輸入,對(duì)輸入端可并聯(lián)上拉或下拉電阻以保證靜態(tài)時(shí)的確定電平。輸出引腳 1Y、2Y 為高電平有效 TTL 輸出,當(dāng) G 使能且地址與輸入選中對(duì)應(yīng) C 線時(shí),將選中線路上的數(shù)據(jù)通過緩沖器驅(qū)動(dòng)到 Y 引腳,輸出電流可達(dá) ±8mA,滿足大多數(shù)中小負(fù)載驅(qū)動(dòng)需求。

VCC 引腳需穩(wěn)定提供 +5V 電源,且在電源端并聯(lián) 0.1μF 陶瓷旁路電容與 10μF 電解電容,用于濾除電源噪聲與瞬態(tài)干擾。GND 引腳為所有邏輯信號(hào)的參考地,PCB 設(shè)計(jì)時(shí)應(yīng)鋪設(shè)寬地銅皮以降低接地噪聲。

五、主要電氣參數(shù)指標(biāo)

74LS153 的電氣特性是其在各類數(shù)字系統(tǒng)中可靠工作的基礎(chǔ),設(shè)計(jì)時(shí)需詳細(xì)參照數(shù)據(jù)手冊(cè)中提供的各項(xiàng)參數(shù)指標(biāo)。以下為關(guān)鍵參數(shù)概覽:

供電電壓(V<sub>CC</sub>)

芯片典型工作電壓為 +5.0V,允許工作范圍 +4.75V 至 +5.25V。過高的電壓會(huì)導(dǎo)致內(nèi)部肖特基二極管過載,過低的電壓則可能使輸出電平不符合 TTL 標(biāo)準(zhǔn),從而引發(fā)邏輯判斷錯(cuò)誤。

輸入高電平閾值(V<sub>IH</sub>)

在 +25℃ 時(shí),V<sub>IH</sub> 最小需 2.0V 以上才能被識(shí)別為高電平,若應(yīng)用端信號(hào)源電壓偏低,建議在輸入端加緩沖門或上拉電阻,以防止地址或使能端誤判。

輸入低電平閾值(V<sub>IL</sub>)

最大 0.8V 以下才能被可靠地判定為低電平,若輸入線路長、噪聲大,可在信號(hào)源輸出端增加 RC 濾波或施加接地電阻來凈化信號(hào)。

輸出高電平電壓(V<sub>OH</sub>)

在輸出為高電平并驅(qū)動(dòng) -3.2mA 負(fù)載時(shí),V<sub>OH</sub> 下限為 2.7V,保證足夠的上拉電平兼容后級(jí) TTL 或 CMOS。

輸出低電平電壓(V<sub>OL</sub>)

在輸出為低電平并驅(qū)動(dòng) +8.0mA 負(fù)載時(shí),V<sub>OL</sub> 上限為 0.5V,保持清晰的低電平狀態(tài),避免誤觸發(fā)后級(jí)器件。

靜態(tài)電流消耗(I<sub>CC</sub>)

每通道在 G=“0” 且地址任意狀態(tài)時(shí),典型靜態(tài)電流約 8mA;若 G=“1”(輸出高阻),所有輸出全部泄漏時(shí),靜態(tài)電流約 4mA。大量并聯(lián)使用時(shí),需評(píng)估整體功耗并配備足夠的旁路電容。

開關(guān)時(shí)序參數(shù)

包括地址到輸出的傳輸延遲(t<sub>PZH</sub>/t<sub>PZL</sub>)和使能到輸出的使能延遲(t<sub>EHZ</sub>/t<sub>EZH</sub>)等,典型值在 20ns 至 45ns 區(qū)間。若在 20MHz 以上系統(tǒng)中使用,需要結(jié)合仿真與示波器測(cè)量確認(rèn)時(shí)序裕量。

全面掌握以上各項(xiàng)參數(shù),能夠讓設(shè)計(jì)者在 PCB 布局、時(shí)序匹配、功耗管理與信號(hào)完整性等方面做出精準(zhǔn)判斷,確保 74LS153 在整個(gè)系統(tǒng)中穩(wěn)定且高效地運(yùn)行。

六、時(shí)序特性

多路復(fù)用器的核心特征在于地址變化或使能改變后,數(shù)據(jù)從輸入切換到輸出所需的時(shí)間。74LS153 在典型條件(V<sub>CC</sub>=5V、T<sub>j</sub>=25℃)下,其時(shí)序特性如下:

地址到輸出有效延遲(t<sub>PZH</sub>、t<sub>PZL</sub>)

當(dāng)?shù)刂?A、B 任一路從“0”切換到“1”或“1”切換到“0”時(shí),C→Y 路徑傳輸延遲通常在 30ns 左右,最快可達(dá) 20ns,最慢不超過 45ns。此延遲包括內(nèi)部 TTL 緩沖門的傳播時(shí)間與肖特基二極管恢復(fù)時(shí)間。

使能到輸出關(guān)閉延遲(t<sub>EHZ</sub>、t<sub>EZH</sub>)

當(dāng) G 從“0”切換到“1”時(shí),輸出進(jìn)入高阻態(tài),此過程約需 25ns;當(dāng) G 從“1”切換到“0”時(shí),輸出恢復(fù)正常(隨當(dāng)前地址選擇輸入),此過程約需 30ns。高阻態(tài)切換對(duì)于總線多路共享尤為重要,需要精確控制槽口時(shí)間,以防出現(xiàn)總線沖突。

輸出有效保持時(shí)間(t<sub>H</sub>)

在地址或使能信號(hào)切換后,輸出保持先前狀態(tài)的時(shí)間約為 10ns,若后級(jí)存在寄存器接收,則需確認(rèn)捕獲窗不受抖動(dòng)影響。

故障模式時(shí)序(t<sub>F</sub>)

當(dāng)?shù)刂沸盘?hào)存在毛刺或使能信號(hào)偶發(fā)跳變時(shí),輸出可能出現(xiàn)短暫的錯(cuò)誤脈沖,此毛刺寬度通常低于 5ns,但足以對(duì)高速采樣器件造成誤觸發(fā),應(yīng)在設(shè)計(jì)中加以濾除或使用多級(jí)觸發(fā)器抖動(dòng)抑制。

通過示波器在真實(shí)電路環(huán)境下捕獲各路徑的上升沿和下降沿時(shí)間,并對(duì)比數(shù)據(jù)手冊(cè)值,可以驗(yàn)證所選 PCB 走線、去耦與終端電阻等設(shè)計(jì)是否滿足系統(tǒng)時(shí)序需求。若測(cè)量值接近或超出規(guī)范上限,應(yīng)考慮在輸入端增加快速施密特觸發(fā)緩沖器或在輸出端采用阻容阻尼網(wǎng)絡(luò)以改善信號(hào)過渡速率。

七、典型應(yīng)用示例

74LS153 在數(shù)字電路中應(yīng)用廣泛,以下列舉幾種最具代表性的場(chǎng)景:

? CPU 總線復(fù)用

在片上或片間總線設(shè)計(jì)中,74LS153 可用來復(fù)用數(shù)據(jù)或地址線。通過兩路使能引腳,可在片上存儲(chǔ)器和外部 I/O 之間快速切換同一組物理線,從而節(jié)省 PCB 空間并簡化布線。典型電路中,G1、G2 分別由片上存儲(chǔ)器讀寫信號(hào)和 I/O 訪問信號(hào)控制,當(dāng)讀存儲(chǔ)時(shí),存儲(chǔ)器數(shù)據(jù)經(jīng) 1C0–1C3 路由至總線;當(dāng)訪問 I/O 時(shí),I/O 端口通過 2C0–2C3 輸出至總線。

? 視頻信號(hào)選擇

對(duì)于多路復(fù)合視頻信號(hào)(CVBS)、YUV 分量或 RGB 通道的切換,74LS153 能在微秒級(jí)內(nèi)完成通道切換而對(duì)畫面無閃爍影響。地址由數(shù)模轉(zhuǎn)換器(DAC)或 TTL 邏輯生成,使能信號(hào)與場(chǎng)中斷(VBI)同步,從而在場(chǎng)消隱區(qū)安全切換。

? 測(cè)試與測(cè)量設(shè)備

在自動(dòng)測(cè)試設(shè)備(ATE)或示波器前端,需要對(duì)多路被測(cè)信號(hào)進(jìn)行采樣與比較。74LS153 可將被測(cè)信號(hào)按通道集中接至高速比較器或 ADC,地址由微控制器驅(qū)動(dòng),通過連續(xù)快速掃描完成多點(diǎn)測(cè)試或多路仿真。

? 音頻信號(hào)路由

在專業(yè)音頻處理器中,74LS153 可做為高阻隔離的低阻帶路開關(guān),用于在不同音源或不同處理路徑間進(jìn)行切換。由于 TTL 輸出具備±8mA 驅(qū)動(dòng)能力,可直接驅(qū)動(dòng)小功率耳放或差分轉(zhuǎn)換器,節(jié)省額外開關(guān)芯片。

八、PCB 布局與信號(hào)完整性優(yōu)化

在高速數(shù)字電路中,74LS153 的性能不僅取決于器件本身的電氣特性,還深受印制板布局與走線策略的影響。首先,應(yīng)保證 V<sub>CC</sub> 與 GND 的去耦電容緊貼芯片電源腳,推薦在 VCC(16 腳)與 GND(8 腳)之間并聯(lián)一顆 0.1 μF 陶瓷旁路電容和一顆 10 μF 電解電容,以濾除高頻和低頻干擾。旁路電容應(yīng)放置在最短路徑,焊盤之—與芯片引腳間距不超過 5 mm,否則濾波效果會(huì)大幅下降。

其次,信號(hào)走線應(yīng)遵循“短、直、粗”原則。地址輸入 A1、B1、A2、B2 及使能 G1、G2 為時(shí)序敏感信號(hào),建議加敷銅層或走多條平行線以降低傳輸阻抗和串?dāng)_。若周邊還有其他高速器件,需在 74LS153 的信號(hào)走線與其他走線之間留出至少 5 倍線寬的間距,以減少電容耦合與互感干擾。對(duì)于長距離連接,應(yīng)在線路兩端添加適當(dāng)阻尼電阻(22 Ω~47 Ω),緩和信號(hào)邊沿,抑制反射。

再次,為防止地彈(ground bounce)影響邏輯判斷,地線應(yīng)采用整面銅箔,并在芯片地腳周圍布置“地溝”或地環(huán),形成低阻抗回流路徑,使大電流回流集中于局部,避免沿板面擴(kuò)散。若電路板為多層結(jié)構(gòu),建議將芯片置于靠近電源層與地層的信號(hào)層上方,這樣走線時(shí)可以自上而下形成“微帶線”結(jié)構(gòu),信號(hào)參考平面穩(wěn)定,有助于改善信號(hào)完整性。

最后,若在同一系統(tǒng)中存在高速總線或差分信號(hào),如 PCIe、LVDS 等,應(yīng)將 74LS153 及其走線與這些高速通道隔離放置;同時(shí)在芯片周圍增加“隔離區(qū)”并可加裝 EMI 濾波器件(如共模扼流圈或 π 型濾波網(wǎng)絡(luò)),有效抑制來自外部或內(nèi)部的電磁輻射,確保 74LS153 在噪聲環(huán)境中依然能夠保持清晰可靠的多路復(fù)用功能。

九、故障分析與調(diào)試方法

當(dāng) 74LS153 在電路中出現(xiàn)功能異常時(shí),需要系統(tǒng)化地分析與定位故障。首先可通過示波器探測(cè)各輸入引腳的電平,確認(rèn)使能腳 G1、G2 是否處于正確的低電平狀態(tài),地址腳是否有抖動(dòng)或毛刺。如發(fā)現(xiàn)地址或使能信號(hào)在切換瞬間出現(xiàn)雜波,應(yīng)檢查上游邏輯或緩沖門,并在必要時(shí)增加 RC 濾波或施密特觸發(fā)器來提高信號(hào)潔凈度。

其次,對(duì)應(yīng)通道的輸出腳 1Y、2Y 若長時(shí)間保持高阻或電平錯(cuò)誤,可使用數(shù)字多用表測(cè)量輸出腳對(duì)地電阻,判斷是否存在內(nèi)部短路或開路。若測(cè)得內(nèi)部短路,應(yīng)立即斷電并更換芯片;若為開路,則需檢查 PCB 焊接質(zhì)量及走線是否斷裂。對(duì)于間歇性故障,可在輸出腳與地或電源之間串接小電阻(100 Ω),利用示波器捕捉瞬態(tài)電流波動(dòng),判斷故障是否與負(fù)載短路或過流保護(hù)觸發(fā)相關(guān)。

第三,可進(jìn)行時(shí)序測(cè)試。通過在地址與使能端加上已知的方波信號(hào),調(diào)整頻率,并利用雙通道示波器同時(shí)觀測(cè)相應(yīng)的輸出響應(yīng)。若輸出的延遲或保持時(shí)間超出規(guī)范,可判定 PCB 走線長度或去耦不足,導(dǎo)致內(nèi)部緩沖門驅(qū)動(dòng)能力下降;也可能是芯片老化或受潮引起泄漏電流增加,建議更換新品進(jìn)行對(duì)比測(cè)試。

最后,常見的故障還包括受熱引起的參數(shù)漂移及失效。可在故障復(fù)現(xiàn)時(shí)測(cè)量芯片結(jié)殼溫度,若超出 74LS 系列安全范圍(–55 °C 至 +85 °C),需改進(jìn)散熱設(shè)計(jì)或降低周圍熱源功率;必要時(shí)也可在調(diào)試階段對(duì)芯片進(jìn)行恒溫箱測(cè)試,以排除環(huán)境溫度對(duì)性能的影響。通過上述步驟,往往能快速定位故障根因,并采取相應(yīng)的電路修正或器件更換,恢復(fù)系統(tǒng)穩(wěn)定運(yùn)行。

十、替代型號(hào)及擴(kuò)展電路設(shè)計(jì)

在某些項(xiàng)目中,設(shè)計(jì)者可能因功耗、速度或封裝限制而選擇 74LS153 的替代品。若需要更低功耗與更高集成度,可考慮 74HC153 或 74HCT153,它們?cè)陟o態(tài)功耗方面遠(yuǎn)低于 LS 系列(靜態(tài)電流僅數(shù)十微安),但輸出電平兼容 TTL。若對(duì)切換速度要求極高,可選用 74F153(快速 TTL),其傳播延遲可低至 10ns,但靜態(tài)功耗相對(duì)增大。

在多路復(fù)用與解復(fù)用需求同時(shí)存在的場(chǎng)合,可將兩片 74LS153 級(jí)聯(lián)使用,將 2Y 輸出之一反向后作為另一片的使能輸入,實(shí)現(xiàn)一級(jí)復(fù)用與二級(jí)解復(fù)用一體化設(shè)計(jì);或者與 三態(tài)總線收發(fā)器(如 74LS245)配合,將選通后的數(shù)據(jù)放大驅(qū)動(dòng)總線,從而構(gòu)建更大規(guī)模的可編程數(shù)據(jù)路由矩陣。

此外,74LS153 還可與模擬開關(guān)(如 CD4066)結(jié)合,構(gòu)成數(shù)字—模擬混合開關(guān)網(wǎng)絡(luò)。將數(shù)字地址信號(hào)驅(qū)動(dòng) 74LS153,同時(shí)利用其輸出邏輯作為控制信號(hào),開啟相應(yīng)的 CD4066 通道,從而完成對(duì)模擬音頻或視頻信號(hào)的選通。該混合設(shè)計(jì)在多媒體切換系統(tǒng)、自動(dòng)測(cè)試平臺(tái)中具有重要應(yīng)用價(jià)值。

十一、仿真工具性能預(yù)測(cè)與驗(yàn)證

在產(chǎn)品開發(fā)早期,可利用仿真軟件對(duì) 74LS153 的性能進(jìn)行預(yù)測(cè)與驗(yàn)證。常用工具包括 SPICE 或 Mentor Graphics HyperLynx。在 SPICE 模型中,應(yīng)準(zhǔn)確引用芯片廠商提供的宏模型,包含內(nèi)部肖特基二極管與 TTL 緩沖門元件,以模擬真實(shí)的開關(guān)延遲、毛刺行為及電源噪聲影響。

通過在 SPICE 中搭建多路復(fù)用測(cè)試平臺(tái),可施加不同頻率與幅值的地址與使能信號(hào),觀察輸出腳的傳輸延遲、毛刺寬度及電平擺幅。若仿真結(jié)果與數(shù)據(jù)手冊(cè)相差較大,需核對(duì)模型參數(shù)或在 PCB 級(jí)別增加寄生電容與走線電感進(jìn)行更精確建模。

使用 HyperLynx 等專門的信號(hào)完整性工具,則可對(duì)走線進(jìn)行時(shí)域反射分析(TDR)與串?dāng)_仿真,評(píng)估在 50 Ω 鏈路下輸出信號(hào)的完整性。借助仿真結(jié)果,設(shè)計(jì)者可優(yōu)化阻尼電阻位置、調(diào)整走線間距與層疊結(jié)構(gòu),提前預(yù)見高頻運(yùn)行時(shí)可能出現(xiàn)的信號(hào)畸變與互干擾。

十二、結(jié)論

74LS153 作為經(jīng)典的雙 4 選 1 TTL 多路復(fù)用器,以其成熟可靠、易于獲取和低成本的優(yōu)勢(shì),在數(shù)字電路設(shè)計(jì)中扮演重要角色。從引腳功能與電氣參數(shù),到 PCB 布局與信號(hào)完整性,再到故障分析、替代型號(hào)與仿真驗(yàn)證,全方位的理解和實(shí)踐可以幫助工程師將該器件的性能優(yōu)勢(shì)最大化地應(yīng)用于各類復(fù)雜系統(tǒng)。通過合理的去耦、走線與濾波設(shè)計(jì),結(jié)合 SPICE 與信號(hào)完整性仿真工具,既可實(shí)現(xiàn)高達(dá)數(shù)十兆赫茲的開關(guān)速度,又能保持低功耗與穩(wěn)定數(shù)據(jù)傳輸,為現(xiàn)代電子產(chǎn)品提供可靠的多路數(shù)據(jù)選通解決方案。

1、本文內(nèi)容、數(shù)據(jù)、圖表等來源于網(wǎng)絡(luò)引用或其他公開資料,版權(quán)歸屬原作者、原發(fā)表出處。若版權(quán)所有方對(duì)本文的引用持有異議,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com),本方將及時(shí)處理。

2、本文的引用僅供讀者交流學(xué)習(xí)使用,不涉及商業(yè)目的。

3、本文內(nèi)容僅代表作者觀點(diǎn),拍明芯城不對(duì)內(nèi)容的準(zhǔn)確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨(dú)立判斷做出的,請(qǐng)讀者明確相關(guān)結(jié)果。

4、如需轉(zhuǎn)載本方擁有版權(quán)的文章,請(qǐng)聯(lián)系拍明芯城(marketing@iczoom.com)注明“轉(zhuǎn)載原因”。未經(jīng)允許私自轉(zhuǎn)載拍明芯城將保留追究其法律責(zé)任的權(quán)利。

拍明芯城擁有對(duì)此聲明的最終解釋權(quán)。

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)