pcie總線接口信號是什么?

6

6

拍明芯城

拍明芯城

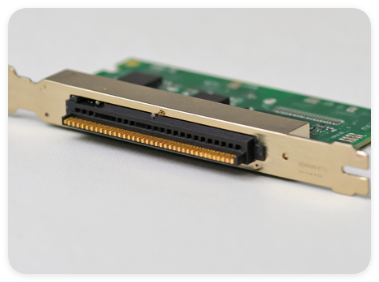

PCIe總線接口信號主要包括以下幾類:

時鐘信號:

REFCLK+和REFCLK-:PCIe設備和PCIe插槽都具有REFCLK+和REFCLK-信號,用于與處理器系統同步。PCIe插槽使用這組信號與處理器系統同步,其頻率范圍為100MHz±300ppm。

SMCLK:與x86處理器的SMBus相關,用于管理處理器系統的外部設備,并收集外設的運行信息。

復位信號:

PERST#:全局復位信號,由處理器系統提供,用于復位PCIe插槽和PCIe設備。PCIe設備使用該信號復位內部邏輯。

電源信號:

Vcc:主電源,用于PCIe設備使用的主要邏輯模塊。

Vaux:輔助電源,與電壓管理相關的邏輯使用,一些特殊的寄存器使用Vaux供電。

輔助信號:

WAKE#:當PCIe設備進入休眠狀態,主電源已經停止供電時,PCIe設備使用該信號向處理器系統提交喚醒請求。

PRSNT1和PRSNT2:用于PCIe設備的熱拔插,通過特定的金手指結構實現設備的熱插拔功能。

數據信號:

PCIe總線使用差分信號進行數據傳輸,每個Lane由一對Rx、Tx差分對組成。PCIe鏈路可以由多條Lane組成,目前PCIe鏈路可以支持1、2、4、8、12、16和32個Lane。

其他信號:

JTAG信號:用于芯片內部測試,包括TRST(復位信號)、TCK(時鐘信號)、TDI(數據輸入)、TDO(數據輸出)、TMS(模式選擇)。

SMBus信號:用于管理處理器系統的外部設備,并收集外設的運行信息。

這些信號共同構成了PCIe總線接口,實現了高速、高效的數據傳輸和設備間的通信。PCIe總線接口信號的設計和優化對于提高系統的性能和穩定性至關重要。

責任編輯:Pan

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)