AP1302協處理器

AP1302協處理器

相關文章 : 1篇

瀏覽 : 21次

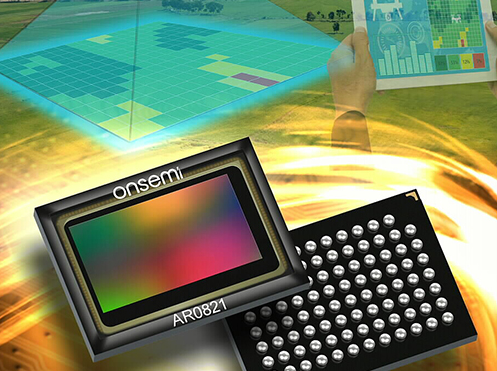

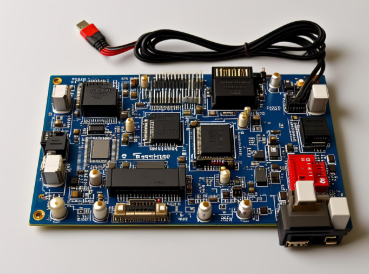

通過使用標準的96Boards方案,所以可以方便利用Xilinx Ultra96-V2平臺的功能來實現低延遲視覺系統原型。 該平臺采用MIPI和攝像機串行接口(CSI2),這是MIPI聯盟的規范。MIPI-CSI2規范定義了圖像傳感器、ISP和主機處理器之間的接口,并用于大多數嵌入式系統中圖像傳感器的高速通信輸出。 On Semi的api1302 ISP可執行包括傳感器的轉動、配置和校準等圖像處理功能,這些處理功能也有助于減少開發嵌入式攝像機系統的工作量。AP1302使用MIPI-CSI2通道連接傳感器和主機處理器。

推薦產品

列表欄目

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)